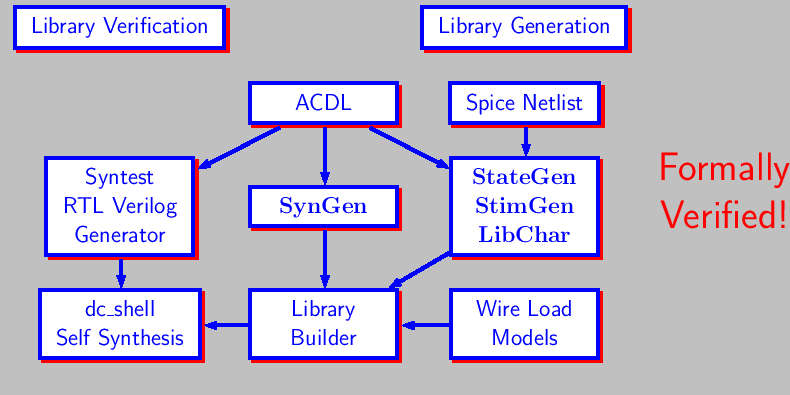

SynGen synthesizes a Liberty model complete with function, timing and power information. Along with the other LTI tools, StimGen, LibChar and SynTest, it makes a complete liberty library builder. After the characterization process is completed, a thoroughly tested and verified Liberty library could be built from scratch in a matter of minutes. Another LTI utility, MakeLib, keeps track of the individual steps involved in library creation. The command

makelib libertylibraryis all that is needed. All model generators use ACDL

For Liberty libraries NLDM table lookup based timing and power library is the default. One can enable signal integrity characterization and pass noise immunity and noise propagation data to be generated and passed over to liberty library. Signal integrity information is only generated in NLDM format for use by PrimeTime.

LTI tools also support current source models, CCS and ECSM. Both of these formats can co-exist in the same library. MakeLib generates test-bench circuits for checking the accuracy of CCS and ECSM based delay calculation for each timing path of the cells for user specified RC networks used as loads. Spice based simulation results are then compared to what may be reported by PrimeTime(TM) and other delay calculators.

LTI tools also support CCS-Power models where supply currents are reported for each input switching in CCS format. This also entails generation of various information for multiple-supply designs.

There is an automated flow for making sure that liberty model and circuit level implementation are functionally equivalent. Such tests are only meaningful for cells which can be inferred during synthesis. It does not work for memories, for example.

VeriGen synthesizes a Verilog Model complete with timing and functionality, using ACDL description as the primary input. A structural model is synthesized using Verilog built-in primitives. Primitives are supplanted with a few UDP's to model sequential elements. The structural model is optimized for faster simulation, and reduced run-time memory.

The electrical parameters of the model are also inferred from the ACDL description of the cell. The new model can be verified for functional correctness using VeriTest, which generates test vectors and expected outputs for the model. The models are an accurate representation of the ACDL statement. Illegal inputs are captured, and generate “x” during simulation.

Liberty and Verilog models have consistent set of timing parameters. This is necessary for SDF back-annotation. MakeLib can test SDF compatibility between liberty a verilog libraries for different SDF generators.

VeriGen can generate different flavors of libraries:

VitalGen

can synthesize a VITAL compliant VHDL Model

complete with timing and functionality.

The new model can be verified for

functional correctness using VitalTest, which generates test

vectors and expected outputs for the model in a

VHDL model ready for simulation. This test-bench instantiates the newly created

model, and if there is any mismatch against the expected behavior,

it will report it.