UnBlock is a library generator for Structured Custom Layout

Blocks. These blocks are usually handcrafted, don't use an ASIC library,

and usually take advantage of circuit and layout techniques which are

normally avoided in standard cell designs. The main problem with these

blocks is the difficulty of functional and timing verification. Transistor

level timing and functional simulators are the only available tools

designers can rely on. It is difficult to prepare inputs for them,

simulation times are too long and are more buggy compared to standard

ASIC design tools. UnBlock removes this handicap of the custom choice,

by generating a cell library with which the structured custom block

can be simulated with. With a standard cell type library, it becomes

possible to use timing analysis and simulation tools at a higher level

than transistor level.

The user identifies the generic functional units inside the block as ACDL

templates. The structured SPICE netlist is scanned by UnBlock looking

for variations of the generic function, and writes out circuit files for

each of the functional instantiations, and a specific ACDL file for the

new cell. With these two outputs, library generators in Libtech's tool

suite can take over to generate a custom library for the custom block.

UnBlock is a library generator for Structured Custom Layout

Blocks. These blocks are usually handcrafted, don't use an ASIC library,

and usually take advantage of circuit and layout techniques which are

normally avoided in standard cell designs. The main problem with these

blocks is the difficulty of functional and timing verification. Transistor

level timing and functional simulators are the only available tools

designers can rely on. It is difficult to prepare inputs for them,

simulation times are too long and are more buggy compared to standard

ASIC design tools. UnBlock removes this handicap of the custom choice,

by generating a cell library with which the structured custom block

can be simulated with. With a standard cell type library, it becomes

possible to use timing analysis and simulation tools at a higher level

than transistor level.

The user identifies the generic functional units inside the block as ACDL

templates. The structured SPICE netlist is scanned by UnBlock looking

for variations of the generic function, and writes out circuit files for

each of the functional instantiations, and a specific ACDL file for the

new cell. With these two outputs, library generators in Libtech's tool

suite can take over to generate a custom library for the custom block.

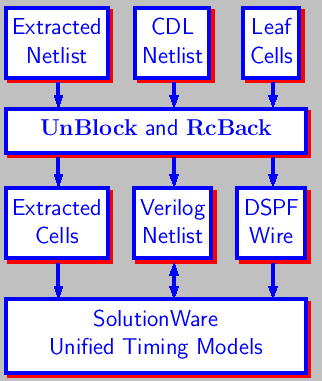

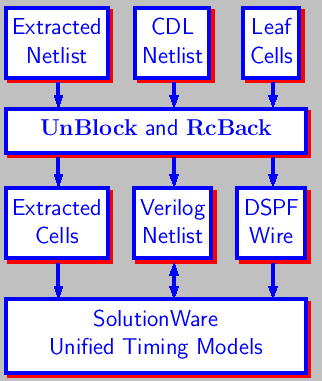

RcBack takes as its input an extracted flat netlist along with the CDL file and splits it into extracted cells identified by UnBlock and DSPF or lumped capacitance files for the interconnect wiring between the cells. Back-annotated circuit files can be re-characterized for maximum accuracy and new libraries can be rebuild using MakeLib. The user can optionally select to have the interconnect be merged inside the cells, essentially creating a new cell out of every instance.

UnBlock also generates a new Verilog netlist, which references the cells in the custom library. With the availability of a gate level library, one can speed up block functional verification process by orders of magnitude compared to transistor level tools. Also timing analysis can be performed faster using the more accurate models.

Using UnBlock various custom layouts can be modeled, including

memories, state machines, various hard cores etc. By unifying the

verification flow around the gate level simulators, users can save time,

and streamline the design flow, and achieve a uniform accuracy across

the chip. It automatically monitors the changes in the input netlist,

incrementally updating its outputs. It has been used effectively in

porting and verifying a RISC engine, an MPEG decoder, various complex

cells. For memories, it is better to use LibChar directly along with

a fast spice simulator.