PowerTeam: Gate Level Power Simulator

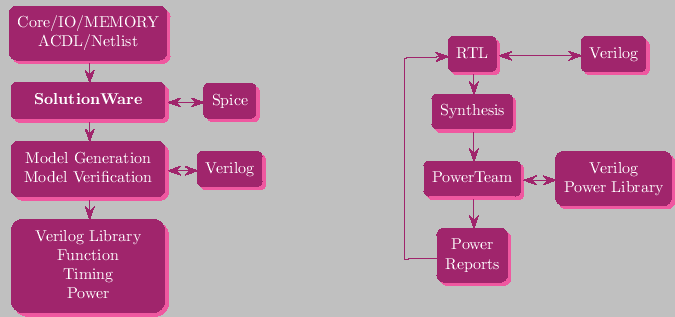

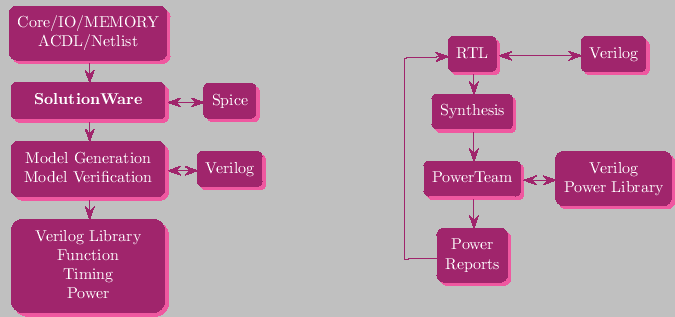

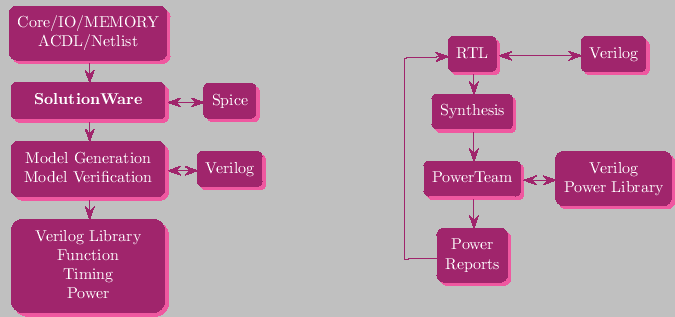

Power Simulation in Verilog

PowerTeam is a dynamic power simulator. It is integrated with Verilog

and provides power simulation and analysis capabilities to Verilog

on top of Verilog's functional and timing simulation capabilities.

Interface to Verilog is through PLI. Verilog-XL and VCS are supported.

In addition to PLI interface, power simulation requires a power

library which describes different power dissipation modes of the

library elements. Various power dissipation parameters are also

contained in this library.

Cell Based Power Models

Unlike other power simulation tools, PowerTeam is “cell” based, where power characteristics of an ASIC

cell are behaviorally modeled just as its functionality. Most other

gate level power simulation tools confine themselves to the

periphery of the

cells. They ignore what may be going on inside or they try to

match the simulation vectors to guess what input changes triggered

what outputs and try to correlate them to a timing/power vector.

Behavioral

modeling allows taking into account the “state” of the cell

during power simulation. The power models are automatically synthesized

into Verilog by VeriGen which analyzes all possible power dissipation

scenarios and generates Verilog code which will activate them

as the situation arises during simulation. Power models can be generated

by SolutionWare tools for standard cells, IO cells with multiple

supplies, and for memories. This makes whole chip dynamic power

simulation a reality so long as the chip can be simulated in Verilog.

PowerTeam is a very accurate power simulator. This is because a

very detailed power characterization of the cell is performed

using SPICE. That includes not only output switching energy dissipation, but includes input switching energy dissipation, which happens a lot more frequently. In addition, PowerTeam can tract the duration of each power event. All significantly different power dissipation modes

are identified by StateGen, and LibChar measures the power dissipated

as the load and input slew changes. Switching energies are calculated

using a two dimensional look-up table. By increasing the number of entries

in the tables, the accuracy of the results can controlled. The

size of the tables do not slow down the power simulation. SPICE

inputs for measuring power dissipation are generated by StimGen automatically from ACDL inputs. Power events are approximated by

rectangular pulses. Duration of the pulse is also measured by

LibChar during characterization. Although there could be inaccuracies

in instantaneous power dissipation as a result of the pulse approximation, energy dissipation is not dependent on it. As a result, the accuracy of

the total energy dissipation could be as good as what may be obtained from

Spice. Power aware Verilog models for the cells, schedule power

dissipation events to be carried out over a period as inputs

change. These events cover output changes as well as internal

state changes. The latter events dominate in a digital world,

although each one of them consume very little energy, are very

important because of the frequency of their occurrences.

Delay and Power Calculation

Reliable timing simulation is a requirement for reliable power

simulation. PowerTeam includes an integrated delay calculator to

predict the precise times at which inputs will trigger power

events. The loads at the outputs of the gates could be either

estimated based on the fanout tables, or they could be back-annotated

after extraction. After determining the effective loads and input

slopes, power dissipation is calculated for each input event and

timing arc along with the estimated duration of the event. Special

attention is given to simultaneously switching outputs at this stage.

Fast Power Simulation

PowerTeam is integrated into Verilog, industry standard for digital

simulation. Compared to timing simulation, run time of power simulation

is 10X slower. Still, compared to transistor based power simulation

options, it is orders of magnitude faster. In addition, it provides

a lot more detailed information on how the power is being dissipated

which can be quite valuable in power optimization.

Whether you are doing

a timing simulation or a power simulation, there is no change in the

simulation setup. Power events can be monitored using Verilog's

programming capabilities, and the results could be tabulated or

viewed using Verilog's native capabilities.

To monitor power usage of a module, one needs to insert

a monitor into that module:

real staticPower;

real totalPower;

real totalIntEnergy;

real totalCapEnergy;

which report any of total dynamic power, total internal energy use, capacitive

portion of the total energy use. Total energy use is the sum of totalIntEnergy

and totalCapEnergy. As the state of the cells change as a result of changes at its inputs and outputs, the static power dissipation of the cell

changes. Such changes are propagated up through the design hierarchy.

Power monitors can be assigned to different sub-modules using PLI

calls to see detailed power usage of individual modules. In addition,

PowerTeam keeps track of various power parameters and dumps them

on demand or at the end of simulation for all the modules and cells.

Whenever an input toggles, it triggers a power event of a finite

duration. When output toggles, duration is assumed to be the delay

of the last changing output. When there are no outputs changing,

power pulse width measured by LibChar is used. Almost all

alternatives to PowerTeam have no concept of the duration of the

input event if it does not trigger an output. Most of the power

events fall in this category, any peak power reported without

tracking the duration of input events is bound to have large errors.

The power consumption changes occurring as a result of input changes

are propagated up though the design hierarchy. This enables to see

how power is consumed by different models.

Power Reports

PowerTeam reports power dissipation of various modules following

the hierarchy of the design. These reports may be static power

or total energy consumption of each module and its siblings.

Energy consumption can be further split into energy consumed due

to capacitive loading and internal energy consumption. Internal

energy consumption is a measure of the quality of the cell libraries.

It can be used to identify ways to improve the performance of the

cell libraries.

Capacitive energy consumption can be used to direct floor planning

and routing.

RTL Power Optimization

Since PowerTeam requires no change in functional and behavioral

simulation environment, it can be integrated into RTL design flow

and used for interactive power optimization. It requires a cell

library which will be used for synthesis to generate a gate level

netlist. Power dissipation of different modules making up the

TL design can then be reported using the simulation vectors used in

TL verification. Once the most energy consuming component is identified, it can be modified to reduce circuit activity. Process continues until

lower dissipation goals are satisfied. At this stage, wire capacitances

can be estimated. Precise loading is unlikely to effect the energy

consumption profiles of different modules, even if the actual

values change.

centerlineDesign Better Cell Libraries

Cell libraries are typically designed with time to market considerations in mind. A generic library may not be the best choice for implementing

low power/high performance design.

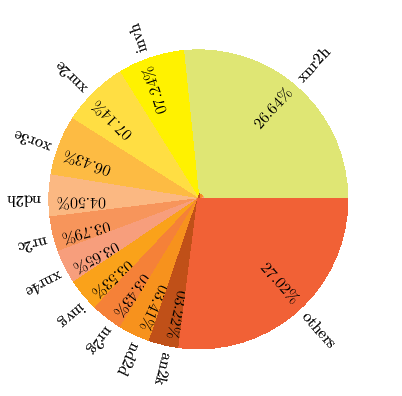

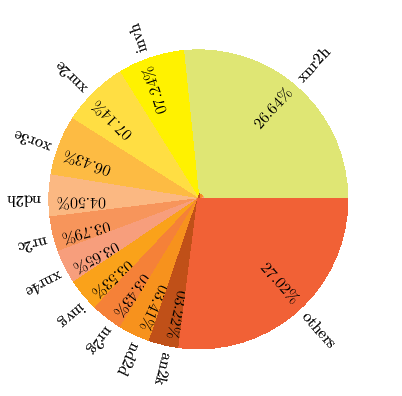

After RTL power optimization possibilities are exhausted, power reports

generated by PowerTeam can be used to identify cells which

are consuming excessive power. For each module, energy consumed by

the cells making up that module can be reported. Such cells can be

redesigned to reduce their power dissipation by CellOpt. If, for example, flip-flops are responsible for 30% of the power consumed by a module,

better lower power flip-flop may significantly reduce the power

dissipation of this module.

Copyright (c) 2019 Library Technologies, Inc., All Rights Reserved.