ChipTimer: Post-Synthesis Design Re-Optimization

A New Paradigm

ChipTimer is a design re-optimization and timing closure tool, to be used for digital designs after synthesis stage, at the gate level.

It can reduce the area and leakage significantly, as well as improve the performance. It is well known that algorithms and architecture

are the most important element of performance, but implementation has

a lot of leeway impacting performance and area of a design. ChipTimer extends the

traditional standard cell based design methodology by simultaneous

design and cell library optimization. In order to achieve these goals,

it uses novel optimization techniques as well as creates new cells and

libraries to implement the design in the most efficient manner. The new

cells and libraries are derived from the existing ones.

ChipTimer can be used both at pre-layout and

post-layout stages of the design process.

Area and Leakage Optimization

ChipTimer has novel algorithms for reducing the area and leakage of a design, making sure that most appropriate cells are used without creating a timing violation. Even after the design is area optimized, as they are out of synthesis, one can get as much as 30% reduction in area and even higher reductions in leakage power. Certainly reduced area improves timing performance as well. The structure of the design is not changed. This step can be invoked at any design stage. Naturally the improvement depends on the choices of cells available in the libraries. The more drive strength, threshold and channel length choices there are, the better the results.

Timing Optimization

Based on the analysis of critical paths, ChipTimer identifies timing

critical cells in the design, and through our circuit optimizer, CellOpt,

it creates faster versions of these cells. Given some timing an load

constraints for a cell, CellOpt can find the most power efficient

implementation of a particular cell. ChipTimer builds new libraries,

and uses the new cells it just created, and keeps iterating as long as

timing of the design can be improved. After it is done, optionally it

re-synthesizes the design to take further advantage of the new cells. At

this point the design may have 10% fewer gates, and almost twice as fast

in clock speed. ChipTimer is very aggressive in timing optimization,

it essentially destroys the critical path wall built by traditional

synthesis tools. A Final area/leakage optimization step slows down all

unnecessarily fast paths, reduces the area, improves the leakage and

further reduces the library size.

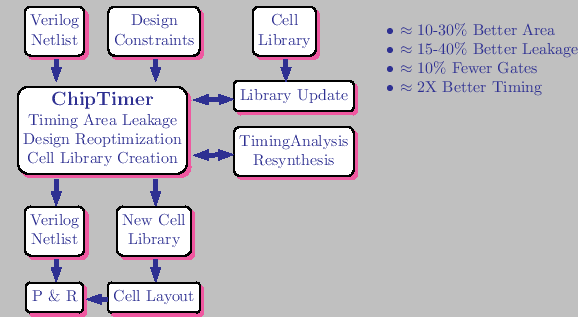

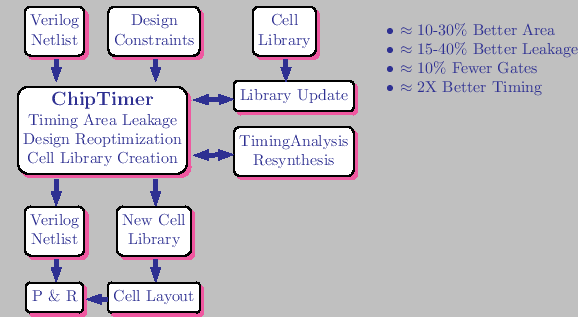

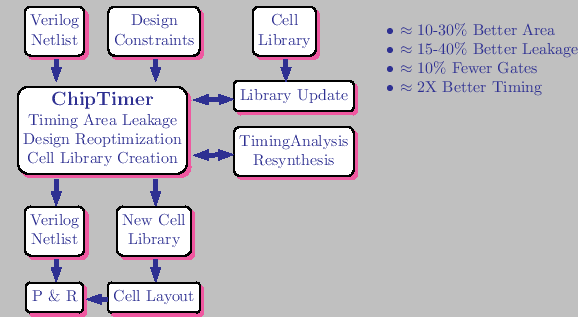

Inputs to and Outputs from ChipTimer

Inputs to ChipTimer are a Verilog netlist, design constraints

and the standard cell libraries.

It produces a new Verilog netlist, new constraint files if there was a structural change in design,

a new set of standard cells, their spice level netlists

and their associated design libraries. Layout level implementation of the new

cells need to be carried out by the user.

ChipTimer Flow

chiptimer integrates together our own optimization algorithms, and also utilizes the capabilities of third party synthesis tools for restructuring the design as may be needed. It utilizes third party timing analysis tools to identify timing critical sections of the design and to assure timing integrity of the design as the design changes. As new cells are needed, they are generated and characterized by MakeLib and CellOpt using industry standard circuit simulators.

The jobs are automatically distributed on a network of machines. Once

library update is completed, design optimization keeps on iterating, typically about five times. Usually, the new cells needed is a fraction of the number of cells used in the design.

ChipTimer interfaces to commercial timing analysis and

synthesis tools. As such, it can handle any digital design, with some minor restrictions on the Verilog netlist format. It uses standard design constraints, appropriate for the synthesis and timing analysis tool. Constraints need to be specified to the boundaries of IO's, memories and analog blocks if any. Each of its capabilities can be invoked at any stage of the design, pre-layout, post-layout to improve or restore timing, area and power characteristics of a design.

Copyright (c) 2019 Library Technologies, Inc., All Rights Reserved.