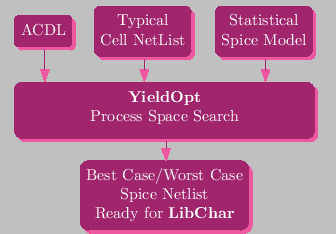

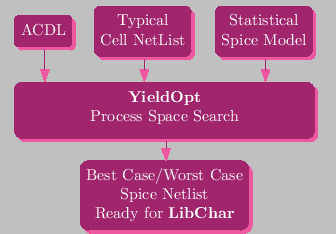

YieldOpt determines the process and OCV state for the best and worst case timing conditions, and generates a new netlist for each cell pertaining to those conditions. It does an exhaustive search within process variation space limited by the yield, or process coverage, specified by the user. All variations are assumed to have a Gaussian distribution. In almost all spice models, such information is available, even if they may not cover correlated variations between various parameters. Principal component analysis is necessary to determine truly independent variables, and reduce pessimism. Once the process and OCV conditions are determined, cell can be characterized to produce various libraries. YieldOpt is integrated into LibChar and other LTI tools through MakeLib. Given a typical condition netlist for each cell, it determines appropriate best/worst case netlist and proceeds with characterization.

YieldOpt helps reduce pessimism inherent in most process models based on 3 process conditions. Especially when variations are relatively large and when device parameters are affected together, best and worst case process corners may not happen at the process extremes. For example, if the width of a device is effectively increased by some process condition, it will improve timing for down stream paths, but may slow down up stream paths. The overall effect depends on the device size and topology. YieldOpt makes a through analysis to account for such effects efficiently. Some process conditions which may be worst case, for a flip-flop, may not be the worst case conditions for an inverter because of different size devices involved and different circuit topology. In the same way, YieldOpt can correct for optimistic best case conditions, by determining such conditions cell by cell.

YieldOpt can perform variational analysis on active as well as passive components. Practically there is no limit on the number of process variables, global or local. When only global variations are considered, its run time is usually a small fraction of characterization time of the cell. When OCV is enabled, it may double or triple the run time compared to characterization. In any case, it is more efficient both for the library creators and as well as for library users. It supports global random variables, which applies to every device, systematic variables which apply to every type of a device, and local random variables which apply to every instance of a device.

YieldOpt provides equivalent functionality to a full Monte-Carlo analysis even for complex cells, exploring all the relevant process space, but much faster. Since timing analyzers are interested only in best or worst case timing, with YieldOpt process variation can be incorporated into traditional design flows. Process coverage needed is specified by the user, and is used to determine the limits of the process space to search for best/worst conditions.

YieldOpt is integrated with MakeLib, and once the user specifies variational parameters for relevant devices, the generated netlists are automatically incorporated into characterization process.